# Computer Architecture PDF (Limited Copy)

John L. Hennessy

Copyrighted Material

John L. Hennessy | David A. Patterson

## COMPUTER Architecture

## **Computer Architecture Summary**

Essential Insights into Modern Computer Architecture Design and Innovation.

Written by New York Central Park Page Turners Books Club

## About the book

In "Computer Architecture: A Quantitative Approach, Sixth Edition," authors John L. Hennessy and David A. Patterson guide readers through the intricacies of computer design, merging theory with practical application. This edition is particularly relevant as it includes the latest advancements in processor and system architecture, which are key in a field marked by rapid technological evolution.

The text kicks off by introducing foundational concepts in computer architecture, establishing the importance of efficient design to optimize performance and energy efficiency. This includes a thorough examination of the RISC-V instruction set architecture, a flexible and open standard that allows for innovation in processor design.

A significant addition in this edition is the in-depth chapter on domain-specific architectures. These specialized designs are critical in addressing challenges posed by the limits of Moore's Law, as we can no longer rely solely on increasing transistor count to drive performance improvements. Instead, domain-specific architectures focus on tailoring systems for particular applications or workloads, enabling greater efficiency.

The authors also delve into the evolving arena of warehouse-scale computing, providing a compelling look at how companies like Google are

reshaping infrastructure to meet the demands of massive data processing.

This section highlights the strategies employed to enhance scalability and resource management in extensive data centers, which serve as the backbone of cloud computing and modern internet services.

Throughout the book, case studies illustrate real-world applications of theoretical concepts, enhancing understanding and retention. Review appendices serve as a valuable resource for readers seeking to reinforce their knowledge of essential topics. With this edition, Hennessy and Patterson maintain the text's status as a crucial reference for educators, students, and industry professionals, ensuring they are well-equipped to navigate the challenges of contemporary computer architecture.

## About the author

In this collection of chapters, the spotlight is on John L. Hennessy, an influential figure in computer science and a trailblazer in computer architecture. The narrative introduces Hennessy's remarkable journey, highlighting his role as a co-author of the seminal textbook "Computer Architecture: A Quantitative Approach." This book has become a foundational resource for countless students and professionals, solidifying Hennessy's legacy in academia.

The chapters delve into the evolution of processor design and performance, particularly emphasizing Hennessy's contributions to RISC (Reduced Instruction Set Computing) architectures. RISC, developed in the 1980s, revolutionized computing by simplifying instructions to enhance processing speed and efficiency. Hennessy's insights and innovations in this area not only advanced theoretical knowledge but also influenced practical applications in the tech industry.

As the former president of Stanford University, Hennessy's impact extends beyond research and textbooks; he has been pivotal in shaping the landscape of computer science education. His leadership at Stanford helped foster a rich environment for technological advancement and innovation, making significant contributions to the development of future generations of computer scientists and engineers.

Throughout the chapters, Hennessy's dedication to his field is underscored by numerous accolades, including the National Medal of Technology and Innovation, which acknowledges his profound influence on technology and education. This chronicle not only showcases Hennessy's professional achievements but also illustrates the interconnectedness of research, education, and industry in driving technological progress. The overarching theme reflects his commitment to excellence and innovation, inspiring readers to appreciate the profound impact one individual can have on an entire discipline.

ness Strategy

7 Entrepreneurship

Self-care

( Know Yourself

## **Insights of world best books**

## **Summary Content List**

Chapter 1: Servers

Chapter 2: Embedded Computers

Chapter 3: The Task of a Computer Designer

Chapter 4: Scaling of Transistor Performance, Wires, and Power in Integrated Circuits

Chapter 5: The Impact of Time, Volume, Commodification, and Packaging

Chapter 6: Cost of an Integrated Circuit

Chapter 7: Cost Versus Price—Why They Differ and By How Much

Chapter 8: 90.7u 12.9s 2:39 65%

Chapter 9: SQRT(EXP(X)) = EXP(X/2)

Chapter 10: Instruction- Level Parallelism and its Dynamic Exploitation

Chapter 11: Exploiting Instruction Level Parallelism with Software Approaches

Chapter 12: Multiprocessors and Thread-Level Parallelism

Chapter 13: 1. split up the longest sections

Chapter 14: 1. Single instruction stream, single data stream (SISD)—This category is the uniprocessor.

Chapter 15: 1. MIMDs offer flexibility. With the correct hardware and software support, MIMDs can function as...

Chapter 16: 1. Communication bandwidth—Ideally the communication bandwidth is limited by processor, memory, a...

Chapter 17: CPI = 0.5 + 0.8 = 1.3

Chapter 18: struct node {/\* a node in the combining tree \*/ int counterlock; /\* lock for this node \*/ int coun...

Chapter 19: Assume that when i processors are in use, the application runs i times faster. Rewrite Amdahl's ...

Chapter 20: One possible approach to achieving the scalability of distributed shared memory and the cost-effe...

Chapter 21: Consider the design of a DSM multiprocessor with 16 processors. Assume the R4400 cache miss overh...

Chapter 22: Assume that we have two DSM multiprocessors: one with CMR support and one without such support. B...

**Chapter 1 Summary: Servers**

The Changing Face of Computing and the Task of the Computer Designer

In the ever-evolving landscape of computing, the role of the computer designer becomes increasingly complex as they navigate various market demands and technological advancements.

**Desktop Computing**

Desktop computing remains the most substantial segment of the market, encompassing a diverse range of systems from budget-friendly models priced under \$1,000 to high-performance workstations exceeding \$10,000. The primary goal in this space is to achieve optimal price-performance ratios; consumers are particularly focused on balancing computational and graphical capabilities with system costs. Notably, desktop systems often serve as the testing ground for cutting-edge microprocessors and innovations. However, as web-centric applications gain traction, they present new hurdles for performance evaluation, complicating traditional metrics. The longstanding reliance on clock rates—shorthand measures of processing speed—may mislead both consumers and designers, obscuring a broader understanding of true system performance.

#### **Servers**

As desktop computing has flourished, the server market has expanded to meet the rising demands of the internet and web-based services. Nowadays, servers function as the foundation of large-scale enterprise computing, effectively replacing older mainframe systems. A primary focus for server design is availability—the capacity to deliver uninterrupted services, rather than mere reliability, which concerns the probability of a system never failing. Strategies to ensure high availability often involve redundancy, allowing systems to continue functioning even when individual components fail. This aspect is especially critical in sectors where server outages can lead to significant operational disruptions and financial losses, as demonstrated by high-profile incidents from major corporations like Yahoo!, Cisco, and eBay. The implications of server downtime underline the necessity for robust design strategies that prioritize consistent service availability.

Together, these facets of computing highlight not only the advancements in technology but also the ongoing challenges and considerations that computer designers must address to meet the needs of consumers and businesses in a rapidly changing digital landscape.

## **Chapter 2 Summary: Embedded Computers**

### Chapter 2 Summary: Computer Systems Overview

In this chapter, we delve into the world of computer systems, focusing on two primary categories: server systems and embedded computers. Each category plays a crucial role in modern technology, and understanding their key features is essential for a comprehensive grasp of computing.

#### **Key Features of Server Systems**

Server systems are designed to handle significant workloads and provide reliable performance under varying demands. Two critical attributes define these systems:

- **Scalability**: The capacity to expand computing resources—such as processing power, memory, storage, and I/O bandwidth—enables servers to adapt to increasing demands. This flexibility is vital for organizations that experience fluctuating workloads.

- **Efficiency**: Unlike general computing systems that prioritize individual request responsiveness, servers focus on high throughput, measured in metrics like transactions per minute. This performance-oriented design

ensures that servers can manage multiple requests simultaneously, crucial for supporting heavy user loads.

#### **Embedded Computers**

Embedded computers, often integrated within other devices, represent a significant and rapidly growing sector of technology. They include microprocessors in everyday items like household appliances, handheld devices, and gaming consoles. Key characteristics include:

- **Operation**: These computers are generally not recognized as standalone systems, functioning quietly to enhance the devices they inhabit.

- **Programming**: Most embedded systems require initial application code loaded into them, with minimal ongoing updates. Performance optimization is frequently undertaken using assembly language, which offers greater control over the hardware.

- **Cost Factors**: Software expenses are integral to the overall costs of embedded systems. Typically, they prioritize performance while operating within tight budget constraints, making cost-effectiveness a primary consideration in their design.

**Performance Requirements in Embedded Applications**

Embedded systems often need to satisfy strict real-time constraints, especially in applications like digital set-top boxes, where tasks must be executed within specific time limits. Performance evaluation typically utilizes established benchmarks, which assess a system's ability to handle both simple and complex tasks efficiently.

#### **Design Considerations**

When designing these systems, several critical factors come into play:

- **Memory and Power**: Minimizing memory usage and power consumption is vital for maintaining cost-effectiveness and enhancing system performance.

- **Architectural Design**: The architecture of an embedded system includes the instruction set architecture (ISA), which serves as the interface between software and hardware. This includes not only the organization of the system but also details like instruction formats and register usage.

#### **Comparison of Different Computing Classes**

To contextualize the various computer systems, we explore the financial range within which they operate:

- **Desktop systems** typically fall within the \$1,000–\$10,000 bracket.

- **Server systems** are priced between \$10,000 and \$10,000,000, reflecting their capabilities and scale.

- **Embedded systems** range significantly from \$10 to \$100,000, highlighting their diverse applications in consumer electronics and industrial environments.

Additionally, the sales figures for microprocessors underscore the health of the market, particularly for embedded devices, with annual sales surpassing one billion units.

In conclusion, this chapter establishes a foundation for understanding the unique attributes of server systems and embedded computers. By exploring their performance metrics, design considerations, and cost factors, readers gain valuable insights into the essential elements that computer designers must navigate in their work.

Chapter 3 Summary: The Task of a Computer Designer

**Chapter 3: Summary of Key Concepts**

This chapter delves into the essential elements of embedded systems, focusing on their design and power optimization, which are critical in the realm of modern computing, particularly for battery-operated devices.

**Embedded Systems and Power Optimization**

Embedded systems, which are specialized computing units designed to perform dedicated functions, often utilize unique instruction sets. These sets are aimed at minimizing both code size and power consumption, thereby enhancing overall efficiency. As many embedded systems are battery-operated, power optimization becomes a vital concern, leading designers to seek cost-effective packaging solutions and forgo traditional cooling methods, such as fans. An emerging trend in this field involves the integration of processor cores with application-specific circuitry. This combination allows for improved performance by leveraging the best of custom hardware alongside standardized processors.

**Approaches to Embedded Problems**

The chapter outlines three primary strategies to address challenges in embedded system design:

- 1. **Custom Hardware with Standard Processors:** Tailoring hardware to work in tandem with commonly used embedded processors for enhanced functionality.

- 2. **Custom Software on Off-the-Shelf Processors:** Developing specialized software using readily available processors to meet specific application needs.

- 3. **Digital Signal Processors (DSPs):** Utilizing DSPs, which are optimized for processing real-time data, paired with bespoke software to tackle complex tasks.

#### **Role of Computer Designers**

Designers of embedded systems face the intricate task of balancing performance, cost, and power consumption in their designs. They must navigate various design facets—including instruction set creation, organizational structure, and implementation challenges such as power demands and cooling solutions. A comprehensive understanding of diverse technologies, ranging from software methodologies to logic design, is paramount to achieving effective optimization in their projects.

## **Functional Requirements in Design**

Defining functional requirements is crucial in ensuring that a computer system can satisfy market needs. Such requirements may involve offering specific support for applications like graphics processing and ensuring compatibility with existing software ecosystems. The choice of instruction set architecture (ISA) is often shaped by the software landscape and prevailing market trends, emphasizing the need for flexibility and adaptability in design.

#### **Changing Metrics in Computer Design**

Different segments of the computing market—such as desktop computers, servers, and embedded systems—prioritize varying metrics for optimization:

- Desktops typically focus on achieving a balance between cost and performance.

- Servers are aimed at maximizing availability and throughput.

- Embedded systems prioritize cost-efficiency and low power consumption.

#### **Technology Trends Impacting Design**

To remain viable in a rapidly evolving technological landscape, successful instruction set architectures must adapt to continuous advancements. Key factors influencing design include:

- Integrated Circuit Logic Technology: The exponential growth in transistor density has significant implications for both performance and

cost-effectiveness.

- **Semiconductor DRAM:** Substantial improvements in DRAM density play a crucial role in shaping memory performance and cost considerations.

This overview encapsulates the main themes of Chapter 3, highlighting the interplay of embedded systems design, the critical importance of power optimization, and the impact of ongoing technological changes on computer architecture.

**Chapter 4: Scaling of Transistor Performance, Wires, and Power in Integrated Circuits**

**Chapter 4 Summary: Technology Trends in Computer Architecture**

Chapter 4 examines the rapid advancements in computer architecture, focusing on several critical areas that influence system performance and design.

#### 1. Advancements in Memory Technology

The chapter opens with a discussion on significant improvements in DRAM (Dynamic Random-Access Memory) interfaces, which have led to enhanced bandwidth capabilities. These developments are crucial for supporting faster data processing, and further details will be explored in Chapter 5.

Additionally, magnetic disk technology has made notable strides with disk density improvements exceeding 100% annually since 1990, resulting in significantly reduced access times, which facilitate quicker data retrieval.

## 2. Networking Technology Developments

Next, the chapter delves into networking technologies, highlighting that performance depends largely on the effectiveness of network switches and

transmission systems. The evolution of Ethernet standards and improvements in Internet infrastructure are pivotal, showcasing a trend of increasing bandwidth that is vital for modern computing needs.

## 3. Impact of Technological Changes on Design

The narrative shifts to design considerations, emphasizing that engineers must account for ongoing technological advancements throughout the product lifecycle. Designers are urged to plan for upcoming generations of technology, particularly in regards to DRAM. Historical trends show a close correlation between technological density improvements and cost reductions, although significant savings can also emerge as abrupt shifts when pressing new thresholds are crossed.

## 4. Integrated Circuit Technology

A major section of the chapter addresses integrated circuit innovations, specifically the scaling down of feature sizes—meaning the dimensions of transistors and wires have decreased dramatically, which contributes to a denser arrangement of transistors and enhanced performance capabilities. As these feature sizes shrink, the density of transistors grows quadratically, improving performance linearly. This advancement has paved the way for the transition from lower-bit to higher-bit microprocessors.

## 5. Wire Delay Challenges

Despite the advantages of smaller transistors, challenges persist, notably with wire delay issues. As feature sizes shrink, wires experience increased resistance and capacitance, leading to heightened signal delays. This

## Install Bookey App to Unlock Full Text and Audio

Free Trial with Bookey

# Why Bookey is must have App for Book Lovers

#### **30min Content**

The deeper and clearer interpretation we provide, the better grasp of each title you have.

#### **Text and Audio format**

Absorb knowledge even in fragmented time.

#### Quiz

Check whether you have mastered what you just learned.

#### And more

Multiple Voices & fonts, Mind Map, Quotes, IdeaClips...

Chapter 5 Summary: The Impact of Time, Volume, Commodification, and Packaging

**Cost and Price Trends in Computer Design**

#### Introduction

The computer industry is currently navigating significant challenges related to power consumption and cost, which are influencing design choices for both supercomputers and more budget-conscious personal computers (PCs). Designers must grasp the intricacies of cost—defined as the expenses involved in producing a product—and price—the retail amount for that product. Recognizing the determinants of cost is crucial for making informed design decisions that balance features and pricing effectively.

## **Relationship Between Cost and Price**

Understanding the interplay between cost and price is essential for computer designers. Cost reflects the investments made in production, while price signifies the final amount customers pay. Designers are tasked with balancing these elements, considering historical and current trends that shape costs over time.

#### The Impact of Time, Volume, Commodification, and Packaging

Several key factors significantly influence the cost dynamics in computer design:

- **Learning Curve:** Over time, manufacturing processes generally become more efficient due to the learning curve effect, which indicates that as production progresses, manufacturers learn to improve yields. A noteworthy example is Dynamic Random Access Memory (DRAM), where prices can plummet by about 40% annually as production efficiencies are realized.

- **Volume:** Increased production volumes facilitate cost reductions through the spreading of development costs across larger units, alongside enhanced manufacturing efficiency. Industry estimates suggest that production costs can decrease by approximately 10% for every doubling of the volume produced, further incentivizing manufacturers to scale up production.

- Commodification: The computer market is experiencing a shift towards commodification, where multiple vendors offer similar products, enhancing competition. This phenomenon tends to drive down costs and aligns them more closely with selling prices, particularly evident within lower-end product segments where products become indistinguishable from

one another.

## **Cost of Integrated Circuits**

Integrated circuits play a pivotal role in the overall system costs of computers. Analyzing the pricing trends of these circuits is essential as they constitute a large portion of the total production expenses. Despite a reduction in manufacturing costs over the years, the underlying production processes for these circuits have remained relatively unchanged, suggesting that while cost efficiencies can be realized, the fundamental methods of production still govern prices.

#### **Conclusion**

The dynamics of cost and price in computer architecture underline the necessity for designers to incorporate economic factors into their design strategies. By comprehensively analyzing trends and understanding the correlations among various influencing factors, computer designers can make informed decisions that will bolster their competitiveness in an increasingly challenging market.

## Chapter 6 Summary: Cost of an Integrated Circuit

### 1.4 Cost, Price, and their Trends

This chapter delves into the intricate relationship between cost and pricing within the semiconductor industry, particularly focusing on Dynamic Random Access Memory (DRAM) and microprocessors—two critical components of modern computing.

#### **Overview of DRAM Prices**

DRAM prices fluctuate closely with supply and demand dynamics, especially during periods of market shortage. Historically, the costs associated with producing DRAM have experienced substantial reductions, with prices decreasing by a factor of five to ten over the lifespan of a product. This trend reflects advancements in manufacturing processes and economies of scale.

#### **Microprocessor Prices**

In contrast to the more straightforward pricing of DRAM, microprocessor prices are influenced by a variety of competitive factors in the marketplace. While prices generally trend downward over time, they rarely fall below the

costs of production due to the complexities and innovations involved in microprocessor design and manufacturing.

#### **Impact of Volume on Cost**

Increasing production volumes can significantly reduce costs through improved manufacturing efficiency. A commonly accepted guideline suggests that costs decrease by approximately 10% with each doubling of production volume. This cost reduction allows manufacturers to align selling prices more closely with production costs, enhancing profitability.

#### **Commodities and Market Trends**

The semiconductor market also encompasses various commodities, such as standard DRAMs and peripherals, that are sold in large quantities by multiple vendors. This intense competition has driven prices down, making low-cost computing more accessible. While the proliferation of low-end computers has improved price-performance ratios, it has resulted in tighter profit margins for manufacturers.

## **Cost of Integrated Circuits**

As integrated circuits become an increasingly significant portion of overall system costs, understanding their pricing structure is vital for computer

architects. The fundamental components of integrated circuit costs include die costs, testing, and packaging. Even as manufacturing costs have plummeted, the processes themselves often retain traditional methods.

#### **Key Factors in Integrated Circuit Costs**

The basic cost structure comprises critical elements such as die yield—the number of usable chips obtained from a wafer—which is influenced by defect density and the complexity of the manufacturing process. Higher defect rates can drastically reduce yield, making it crucial for manufacturers to manage these aspects effectively.

#### **Factors Affecting Die Yield**

Die yield is heavily impacted by manufacturing defects and process complexities. To combat these challenges, designers have started to incorporate redundancy in DRAM designs, allowing for improved yield despite the pressures of pricing competition.

#### **Conclusion**

In the contemporary landscape of chip manufacturing, the design phase is pivotal, as it largely determines die area and production costs. A comprehensive understanding of the interconnections between cost, yield,

and manufacturing processes is essential for optimizing computer designs and ensuring the viability of products in a highly competitive market. This insight not only supports efficient production but also aids in maintaining favorable price-to-performance ratios for consumers.

Chapter 7 Summary: Cost Versus Price—Why They Differ and By How Much

Differ and by How Much

### Summary: Cost, Price, and Their Trends

In exploring the intricate relationship between cost, price, and performance

in computer architecture, several pivotal themes emerge.

1. Cost of Die Production

The production costs of integrated circuits (often referred to as dies) escalate

significantly as the die area increases, following a complex mathematical

relationship, specifically the fifth power. Designers play a key role in

determining die size and, consequently, costs through their choices regarding

the functionality required and the number of input/output (I/O) pins used.

Furthermore, dies must undergo several expensive processes, including

testing and packaging, which substantially contribute to the overall

production cost.

2. Influence of Fixed Costs

In low-volume production scenarios, one of the most considerable fixed

costs is the mask set, which can cost over \$1 million. Masks are essential for

More Free Book

creating intricate designs during the fabrication of high-density circuits, necessitating multiple layers for a successful production. These significant initial costs can notably impact expenses associated with prototyping and debugging phases, making financial planning in this sector increasingly complex.

#### 3. Cost Distribution in Systems

A historical analysis of component costs in a \$1,000 personal computer from 2001 sheds light on how different components contribute to overall expenses. While some components become cheaper over time due to advances in manufacturing and increased competition, others—like packaging and power supplies—present more limited opportunities for cost reduction, highlighting a nuanced view of pricing trends.

#### 4. Cost vs. Price Difference

It's crucial to understand that costs do not directly equate to selling prices. A variety of factors come into play, influencing the final price that consumers encounter. Direct costs—including labor, materials, and warranties—form a significant part of overall expenses, while gross margins account for the company's overhead costs. The average selling price reflects all incurred costs, modified by competitive pressure, market strategies, and the potential for promotional discounts.

#### 5. R&D Investment Impact

Companies often designate a modest portion of their income to research and development (R&D), yet a more substantial investment can yield higher sales and market success. The interplay between costs and prices is highly influenced by market dynamics, where lower-end products usually face fierce competition, resulting in slimmer gross margins.

#### 6. Complexities of Cost/Performance Design

Designers must adeptly balance between high-performance systems, where cost considerations are secondary, and low-cost solutions that may compromise performance. The contemporary market increasingly demands a harmonious blend of cost and performance efficiency, necessitating a nuanced and strategic design approach.

#### 7. Performance Measurement

In discussing performance, the conversation frequently turns to execution time and throughput—essentially, the speed at which machines can complete tasks. Terminology clarity is vital in this context, where "improving performance" is synonymous with enhancing efficiency and reducing execution time, ensuring that stakeholders share a common understanding of

what constitutes high performance in system design.

This comprehensive overview encapsulates the significant considerations around cost, price, and performance in the field of computer architecture, stressing the importance of thoughtful design and strategic decision-making in achieving success in a competitive market landscape.

Chapter 8: 90.7u 12.9s 2:39 65%

**Chapter 8 Summary: Measuring Computer Performance**

**Introduction to Performance Measurement**

To accurately assess computer performance, execution time using real programs is the most reliable measure. Alternative metrics may lead to misleading conclusions about a system's efficiency.

**Types of Time Measurement**

There are various methods of time measurement in computing:

- Wall-clock Time: Encompasses the total time taken for a computing task, including all system overheads.

- **CPU Time:** Represents the time the CPU spends actively processing, excluding any waiting periods due to input/output operations.

- **User vs. System CPU Time:** User CPU time involves the execution of the program itself, whereas System CPU time pertains to the work performed by the operating system on behalf of the program.

**Selecting Programs for Performance Evaluation**

Performance can be evaluated using five types of programs:

- 1. **Real Applications:** Actual software used by end users, which gives the most accurate performance assessment but lacks portability.

- 2. **Modified Applications:** Adjusted versions of real applications to enhance portability or focus on specific performance aspects.

- 3. **Kernels:** Small segments of code derived from real programs that provide insights into performance characteristics.

- 4. **Toy Benchmarks:** Simple programs designed for educational purposes and basic demonstrations of concepts.

- 5. **Synthetic Benchmarks:** Artificially created programs that imitate typical workloads to evaluate performance.

#### **Benchmark Suites**

The **SPEC Benchmarks** are standardized tools designed to measure CPU performance across a variety of applications. Distinctions are made between **Desktop vs. Server Benchmarks** to tailor performance assessments to specific environments.

## **Reporting Performance Results**

For transparency, performance results must be reproducible and should include detailed information about the system configuration. Reports should present both baseline and optimized results to provide a clear picture of

performance improvements.

# **Principles of Computer Design and Performance**

Key principles include:

- 1. **Make the Common Case Fast:** Design choices should prioritize frequent operations that enhance performance.

- 2. **Amdahl's Law:** The overall performance improvement is influenced by how much time a feature is used and the extent of performance enhancement it provides.

# **CPU Performance Equation**

CPU performance is expressed through the following factors:

- Clock Rate

- Clock Cycles per Instruction (CPI)

- Instruction Count

These components interrelate to define how effectively a CPU performs tasks.

**Locality of Reference**

Programs generally exhibit **temporal** and **spatial locality**, meaning they

tend to repeatedly access the same data and nearby data locations. This

behavior can significantly enhance cache performance, reducing access

times.

**Exploiting Parallelism**

Enhancing performance can also be achieved by implementing parallelism at

various levels—whether in the overarching system architecture, specific

instruction execution, or through detailed design changes.

Market Dimensions: Performance and Price-Performance

Evaluating performance alongside price-performance ratios in desktops,

servers, and embedded systems illustrates how different architectures impact

practical applications and cost-effectiveness in real-world scenarios.

**Misconceptions in Performance Measurement**

Common myths include relying solely on clock rate for performance

comparison or evaluating systems based on a single benchmark outcome.

Performance benchmarking must evolve to remain relevant, as synthetic

benchmarks may not accurately predict real-world performance scenarios.

# Conclusion

A thorough understanding of computer performance measurement requires more than reliance on benchmarks; it necessitates a comprehensive grasp of how varying design components interact, leading to enhanced system execution and efficiency.

# Install Bookey App to Unlock Full Text and Audio

Free Trial with Bookey

Fi

ΑŁ

# **Positive feedback**

Sara Scholz

tes after each book summary erstanding but also make the and engaging. Bookey has ling for me.

Fantastic!!!

I'm amazed by the variety of books and languages Bookey supports. It's not just an app, it's a gateway to global knowledge. Plus, earning points for charity is a big plus!

ding habit o's design al growth

José Botín

Love it! Wonnie Tappkx ★ ★ ★ ★

Bookey offers me time to go through the important parts of a book. It also gives me enough idea whether or not I should purchase the whole book version or not! It is easy to use!

Time saver!

\*\*\*

Masood El Toure

Bookey is my go-to app for summaries are concise, ins curated. It's like having acc right at my fingertips!

Awesome app!

\*\*

Rahul Malviya

I love audiobooks but don't always have time to listen to the entire book! bookey allows me to get a summary of the highlights of the book I'm interested in!!! What a great concept !!!highly recommended! Beautiful App

\*\*\*

Alex Wall

This app is a lifesaver for book lovers with busy schedules. The summaries are spot on, and the mind maps help reinforce wh I've learned. Highly recommend!

Chapter 9 Summary: SQRT(EXP(X)) = EXP(X/2)

**Exercises Summary**

**Synthetic Benchmarks**

Synthetic benchmarks, such as Whetstone and Dhrystone, are designed to measure system performance, but they have significant limitations. They do not accurately represent real-world applications, leading to potentially inflated performance results influenced by compiler and hardware optimizations. These benchmarks overlook optimizations that reflect actual program behaviors, often disregarding substantial portions of code. To address these concerns, the authors of these benchmarks recommend reporting results for both optimized and unoptimized code and have established rules to ban certain optimizations to preserve the integrity of the assessments.

**MIPS** as a Performance Metric

MIPS, or Million Instructions Per Second, is commonly used to evaluate the performance of computers. However, it has proven to be a flawed metric for comparing different machines due to its reliance on specific instruction sets, which complicates comparisons across varied architectures. Additionally,

MIPS values can fluctuate significantly when running different programs on the same machine, and there may be an inverse correlation between MIPS ratings and actual performance in floating-point computations, which are crucial in many modern applications.

### **Relative MIPS and Alternatives**

Relative MIPS, though less problematic than absolute MIPS, still presents challenges in accurately reflecting performance. This metric can mislead users because compilers may optimize for particular structures that do not align with common programming patterns, further distorting performance evaluations.

# **Future Chapters Outline**

The upcoming chapters promise a deeper exploration into various topics. Chapter 2 will provide an in-depth look at instruction set architecture and performance metrics. Chapters 3 and 4 will focus on Instruction Level Parallelism (ILP), analyzing strategies for optimizing performance both at runtime and during the compile phase. Chapter 5 will delve into memory system design, highlighting the importance of collaboration between hardware and software components. Chapters 6 and 7 will shift the discussion from CPUs to examine storage systems and interconnect technology, respectively. The final chapter will cover multiprocessors,

addressing the complexities of memory and execution in shared-memory systems.

# **Historical Perspectives**

To enrich each chapter, a historical perspective will trace the evolution of computer technology and notable innovations pertinent to the topics discussed. This historical context will enhance the reader's understanding of the significance of advancements in processor architectures throughout the development of computing.

# **Exercise Examples**

Practical exercises will be included to assess the understanding of performance improvements through various enhancements, explore the complexities of instruction sets, and test various computational scenarios. These exercises aim to reinforce the concepts presented in each chapter, encouraging a hands-on approach to learning.

This summary synthesizes key ideas about benchmarking, performance metrics, and the chapter structure while incorporating engaging exercises designed to solidify comprehension of the material.

# Chapter 10 Summary: Instruction- Level Parallelism and its Dynamic Exploitation

### Summary of Chapter 10: Computer Architecture

# **Instruction-Level Parallelism and Its Dynamic Exploitation**

In this chapter, the focus is on the pivotal role of instruction-level parallelism (ILP) in advancing modern computer architectures and the various strategies devised to leverage it. This concept refers to the ability of a processor to execute multiple instructions simultaneously, significantly enhancing performance.

# **Vector Instructions and Loop-Level Parallelism**

The chapter begins by examining vector instructions, which are designed for vector processors that can process multiple data elements at once. These processors were instrumental in the early days of computing for applications involving large datasets, like scientific computations. However, as technology evolved, vector processors were largely replaced by more sophisticated systems that employ ILP for efficiency.

# **Data Dependence and Hazards**

A critical aspect of maximizing ILP is understanding instruction dependencies, which can hinder parallel execution. Dependencies are categorized into three main types:

- 1. **True data dependences**—where one instruction's output is another's input.

- 2. **Name dependences**—which arise from the use of the same variable name in different instructions.

- 3. **Control dependences**—which are linked to the execution order of instructions based on branching decisions. Understanding these dependencies is essential for effectively managing execution and minimizing hazards, which are obstacles to running instructions in parallel.

# **Dynamic Scheduling and Hardware Enhancements**

The chapter further explores dynamic scheduling techniques that allow processors to rearrange instructions during runtime to minimize stalls caused by hazards. One key method highlighted is **Tomasulo's algorithm**, which employs reservation stations and a reorder buffer to intelligently manage the scheduling of instruction execution, allowing for more flexible and efficient processing.

# **Branch Prediction and Speculation**

Effective branch prediction is crucial for pipeline efficiency, as mispredictions can create significant delays in instruction execution. The chapter discusses how speculative execution—where processors make educated guesses about branch outcomes—can boost throughput by allowing instructions to be executed out of order, leading to smoother processing flows even in the face of uncertainty.

# **Memory Addressing and Instruction Set Design**

A variety of addressing modes are detailed, including displacement, immediate, and register indirect modes. The chapter emphasizes the importance of strategic design choices in instruction sets, wherein simple and regular encoding of instructions can enhance compiler efficiency and overall system performance.

### **Performance Evaluation**

The discussion moves to practical limitations faced by ILP in real-world processors, which are influenced by factors such as window size, issue width, and memory execution patterns. Empirical studies and comparisons between different processors reveal the complexities and challenges inherent in dynamically scheduled pipelines, illustrating how architectural choices significantly affect performance outcomes.

## **Future Directions**

Concluding, the chapter examines future trends in processing technologies, particularly the emergence of multithreaded architectures that combine thread-level parallelism with instruction-level parallelism. This evolution signifies a shift towards more robust processing capabilities, accommodating an increasing demand for computational power.

In summary, this chapter offers a comprehensive exploration of the techniques and architectural strategies that enable the effective exploitation of parallelism within instruction sets while addressing the inherent limitations and future possibilities in processor design.

# Chapter 11 Summary: Exploiting Instruction Level Parallelism with Software Approaches

### Summary of Chapter 11: Instruction-Level Parallelism and its Dynamic Exploitation

## Introduction

This chapter examines instruction-level parallelism (ILP), which is crucial for enhancing processor performance. The discussion is framed by a historical anecdote referencing the America's Cup race, which inspired IBM's research processor, aptly named "America."

# 1. Instruction-Level Parallelism Concepts and Challenges

ILP is defined as the ability to execute multiple instructions simultaneously, a key driver in improving processor throughput. The chapter highlights key techniques for augmenting ILP, underscoring the challenges posed by data and control hazards. It differentiates between dynamic techniques, which rely on hardware, and static techniques, implemented in software.

# 2. Overcoming Data Hazards with Dynamic Scheduling

To address data hazards that can interrupt instruction flow, dynamic

scheduling is introduced. This process allows processors to reorder instructions to optimize execution without violating data dependencies. Examples of specific dynamic scheduling methods are provided, along with algorithms that illustrate their function. The significance of memory disambiguation—ensuring that memory accesses do not interfere—and speculative execution, which anticipates future instruction paths, is also emphasized for boosting performance.

# 3. Reducing Branch Costs with Dynamic Hardware Prediction

The chapter subsequently delves into branch prediction, a strategy critical for minimizing the penalties associated with mispredictions. It examines dynamic predictors that adapt based on runtime behavior and the importance of supporting hardware like branch target buffers (BTBs) that enhance prediction accuracy by maintaining historical data on branch behavior.

# **4. High-Performance Instruction Delivery**

Next, the importance of providing a high-bandwidth instruction stream is discussed, alongside the architectural challenges that come with it. The chapter explores designs that utilize instruction prefetching and BTBs to improve throughput, ensuring that the instruction cache is continuously filled to prevent stalls.

# **5. Dynamic Scheduling in Superscalar Processors**

The chapter moves on to explore superscalar processors, which are capable of issuing multiple instructions per clock cycle. It examines how dynamic scheduling in such architectures enhances instruction throughput through out-of-order execution, where instructions are executed as resources become available rather than strictly in the order they are received.

# 6. Hardware-Based Speculation

The implementation of hardware-based speculation is then discussed, which allows the processor to execute instructions that may not be needed, under the assumption that the predictions will hold true. The role of the reorder buffer (ROB) is highlighted, enabling the processor to maintain precise interrupts while allowing for flexible execution ordering.

### 7. Thread-Level Parallelism

An introduction to thread-level parallelism (TLP) follows, differentiating it from ILP. TLP involves leveraging multiple threads to execute concurrently, particularly in environments where many tasks can run in parallel, offering distinct advantages over exclusively relying on ILP.

# 8. Historical Perspective on ILP and Modern Processors

A historical overview encapsulates the evolution of ILP exploitation techniques, drawing parallels to contemporary architectures. It emphasizes how modern processors, like the Intel IA-64, integrate dynamic scheduling and speculative execution to harness ILP effectively.

# **Concluding Remarks**

The chapter concludes by discussing the delicate balance between different workload types and the need for processor designs that effectively exploit ILP. It points to ongoing challenges and highlights prospective research avenues aimed at improving ILP utilization through advanced hardware and software strategies.

#### **Exercises**

The chapter includes a series of exercises aimed at reinforcing the concepts discussed, covering topics such as data hazards and dynamic scheduling methodologies. These practical problems encourage deeper engagement with the material, solidifying the reader's understanding of ILP.

# Chapter 12: Multiprocessors and Thread-Level Parallelism

Chapter 12 Summary: Arithmetic and Geometric Means, Harmonic Mean Comparison, SPECfp92 Performance Results, and Multiprocessor Limitations

In this chapter, we explore fundamental concepts of means in mathematics and their implications in computer performance evaluation.

The chapter begins with a discussion of the **arithmetic mean**, which is derived by summing two positive integers  $\langle (a \rangle)$  and  $\langle (b \rangle)$  and dividing by two. A pivotal principle established is that the arithmetic mean is always greater than or equal to the **geometric mean** of the same two numbers, which is found by taking the square root of their product. This relationship holds true with equality only when  $\langle (a \rangle)$  equals  $\langle (b \rangle)$ .

Next, the narrative shifts to the **harmonic mean**, relevant in contexts involving rates, such as speed or efficiency. For any two positive rates  $\langle (r \rangle)$  and  $\langle (s \rangle)$ , the arithmetic mean surpasses or is equal to the harmonic mean, with equality occurring exclusively when both rates are identical.

We then turn to SPECfp92 performance results, a benchmarking test for

evaluating the floating-point performance of computer systems. Data from June 1994 is presented, highlighting the computation of SPEC ratios and demonstrating how geometric means are used to summarize performance across different systems. These benchmarks are critical for understanding the speed and efficiency of various computational architectures.

# Install Bookey App to Unlock Full Text and Audio

Free Trial with Bookey

# Read, Share, Empower

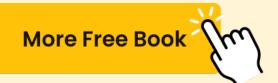

Finish Your Reading Challenge, Donate Books to African Children.

# The Concept

This book donation activity is rolling out together with Books For Africa. We release this project because we share the same belief as BFA: For many children in Africa, the gift of books truly is a gift of hope.

# The Rule

Your learning not only brings knowledge but also allows you to earn points for charitable causes! For every 100 points you earn, a book will be donated to Africa.

# Chapter 13 Summary: 1. split up the longest sections

In Chapter 6, the authors delve into the evolving landscape of computer architecture with a specific emphasis on multiprocessors and thread-level parallelism. They note that while uniprocessor systems have made impressive strides, the future trajectory favors parallel processing due to both economic advantages and the complexities faced by microprocessor architectures.

## **6.1 Introduction**

The chapter opens by underscoring the growing importance of multiprocessors in computing. As uniprocessor performance reaches saturation, multiprocessor systems, with their ability to efficiently manage multiple threads and tasks concurrently, are becoming more relevant.

# **6.2 Characteristics of Application Domains**

Subsequently, the authors explore various application domains such as gaming, scientific computing, and data processing. Each domain has distinct characteristics that influence the architectural choices made in designing multiprocessors, suggesting that a one-size-fits-all approach is inadequate.

# **6.3 Symmetric Shared-Memory Architectures**

The chapter transitions to symmetric shared-memory architectures, where multiple processors have equal access to a common memory space. This structure allows for smooth communication and data sharing among processors, enhancing collaboration and performance.

# **6.4 Performance of Symmetric Shared-Memory Multiprocessors**

To assess the effectiveness of these architectures, the authors discuss key performance metrics, such as throughput and latency. They argue that optimizing these factors is crucial for maximizing the efficiency of symmetric multiprocessor systems.

# **6.5 Distributed Shared-Memory Architectures**

Shifting focus, the chapter examines distributed shared-memory architectures. Unlike symmetric systems, these architectures spread memory across nodes, providing greater scalability and flexibility but introducing complexities in data access and coherence.

# **6.6 Performance of Distributed Shared-Memory Multiprocessors**

The discussion of distributed architectures continues with an analysis of performance capabilities. The authors highlight their ability to handle large

data sets and the challenges of maintaining consistency across distributed nodes.

# **6.7 Synchronization**

A crucial aspect of multiprocessor efficiency involves synchronization mechanisms. The authors explore the necessary techniques for coordinating operations across processors, addressing the inherent challenges in ensuring data integrity and avoiding race conditions.

# 6.8 Models of Memory Consistency: An Introduction

Memory consistency models are introduced to explain how different architectures maintain the order of operations in shared memory environments. These models are fundamental to understanding how multiprocessors read and write data in a reliable manner.

# 6.9 Multithreading: Exploiting Thread-Level Parallelism within a Processor

Building on the discussion of parallelism, the authors delve into multithreading, which allows processors to handle multiple threads of execution simultaneously. This technique enhances resource utilization and improves overall system throughput.

# **6.10 Crosscutting Issues**

The chapter then highlights crosscutting issues that impact multiprocessor design, including hardware limitations and software compatibility, underscoring the multi-faceted challenges architects face in developing robust systems.

# 6.11 Putting It All Together: Sun's Wildfire Prototype

As a practical application of the principles discussed, the authors present Sun's Wildfire prototype. This case study demonstrates how theoretical concepts are applied in real-world multiprocessor systems, showcasing successful implementations in practice.

# **6.13** Another View: Embedded Multiprocessors

Further expanding the discussion, the authors explore embedded multiprocessors, which are tailored for specific applications in environments like consumer electronics and automotive systems. These platforms prioritize specialized performance and efficiency.

### **6.14 Fallacies and Pitfalls**

More Free Book

The chapter also addresses common misconceptions and pitfalls in

multiprocessor architecture design. Acknowledging these frequent errors prepares architects to avoid costly mistakes in their implementations.

# **6.15 Concluding Remarks**

In their concluding thoughts, the authors reflect on the progression of multiprocessor architectures and the balance needed between innovations in uniprocessors and the growing importance of parallel processing.

# **6.16 Historical Perspective and References**

A historical perspective rounds out the chapter, mapping out significant milestones in computer architecture that have shaped the current understanding of multiprocessors.

## **Exercises**

To solidify understanding, the chapter concludes with a set of exercises designed to encourage readers to apply the concepts discussed, fostering a deeper comprehension of the intricacies of multiprocessor architecture.

Chapter 14 Summary: 1. Single instruction stream, single data stream (SISD)—This category is the uniprocessor.

## Introduction

This chapter sets the stage by exploring the different categories of parallel architectures, which are crucial for understanding the diverse design choices that exist in multiprocessor systems. By examining these classifications, readers gain valuable insight into the historical development and the ongoing evolution of multiprocessor technologies.

# **Taxonomy of Parallel Architectures**

The classification framework presented is based on Flynn's taxonomy, established around thirty years ago, which categorizes computers according to their instruction and data processing streams. This model consists of four primary categories:

1. **Single Instruction Stream, Single Data Stream (SISD)**: This category describes classical uniprocessor architectures where a single instruction is processed one data element at a time.

- 2. Single Instruction Stream, Multiple Data Streams (SIMD): In this arc hitecture, multiple processors execute the same instruction simultaneously across different data sets. Each processor operates with its own data memory, while a unified control unit directs the instruction flow. SIMD architectures are commonly seen in multimedia applications and vector processing.

- 3. **Multiple Instruction Streams, Single Data Stream (MISD)**: While no widely-used commercial multiprocessors exist in this category, certain specialized stream processors illustrate this concept by processing a singular data stream through sequential functional units.

- 4. Multiple Instruction Streams, Multiple Data Streams (MIMD): This a rchitecture illustrates a more complex structure where individual processors can fetch their own instructions and handle their own data streams. MIMD systems predominantly include commercial microprocessors and showcase a broad range of operational capabilities, often combining characteristics from other architectures.

The chapter concludes with a historical overview that highlights the trajectory of these categories over time. Initially, SIMD architectures were prevalent, but their popularity waned by the mid-1990s as MIMD systems gained prominence. The ascent of MIMD architectures is attributed to two key developments: advancements in chip technology that support multiple

independent processors, and the increasing demand for flexible and powerful computing capabilities that can handle varied applications efficiently. This shift signifies a transformative period in multiprocessor design, positioning MIMD as the preferred architecture for contemporary general-purpose computing systems.

Chapter 15 Summary: 1. MIMDs offer flexibility. With the correct hardware and software support, MIMDs can function as...

### Chapter 6: Multiprocessors and Thread-Level Parallelism

# 1. Understanding MIMD Architecture

The chapter begins by introducing Multiple Instruction Multiple Data (MIMD) architectures, which are notable for their flexibility and adaptability. These architectures allow multiple processors to operate simultaneously, either as part of a single-user system or within a multiprogrammed environment. By leveraging the cost-performance advantages inherent in standard microprocessors, MIMD systems enable distinct processors to execute separate instruction streams, thereby enhancing computational efficiency.

# 2. Defining Processes and Threads

In the context of MIMD architectures, the chapter differentiates between processes and threads. A process is described as a self-contained segment of code that possesses its own execution state, allowing it to run independently on a processor. In contrast, threads represent multiple execution paths within

a single process, enabling them to cooperate by sharing the same code and address space. This capability opens the door to thread-level parallelism, where the concurrent execution of numerous threads or processes leads to optimized performance.

# 3. Classes of MIMD Multiprocessors

MIMD systems are further classified based on their memory organization into two primary categories. First, **Centralized Shared-Memory Architectures** (also known as symmetric multiprocessors or SMPs) feature a limited number of processors that share a single, centralized memory accessed through a bus system. This setup ensures uniform access times for memory operations, making it suitable for many applications.

In contrast, **Distributed Memory Architectures** involve multiple processors with independently distributed memory units. These architectures are designed to accommodate greater bandwidth needs often required in larger-scale environments. By employing direct and indirect interconnection networks, they facilitate quicker access to local memory while potentially complicating inter-processor communications.

# 4. Communication Models

The chapter concludes by examining the communication models that

underpin data transmission in large-scale multiprocessors, highlighting two main approaches. The **Distributed Shared-Memory (DSM)** model allows processors to interact with separate physical memories as if they were part of a unified logical address space. This setup falls under the non-uniform memory access (NUMA) category, which enables any processor to reference memory, regardless of its physical location.

Conversely, **Multicomputers** operate on the principle of private, disjoint address spaces, with communication occurring through explicit message passing. This model is exemplified by clusters of independent computers, making it an economical choice for applications that require minimal inter-processor communication.

Overall, Chapter 6 provides a comprehensive overview of MIMD architectures, emphasizing their structural diversity, the mechanics of process and thread functioning, and the communication paradigms that facilitate effective data exchange in multiprocessor environments.

# Chapter 16: 1. Communication bandwidth—Ideally the communication bandwidth is limited by processor, memory, a...

# **Chapter 6: Multiprocessors and Thread-Level Parallelism**

This chapter delves into the intricacies of multiprocessor systems and their communication mechanisms, essential for maximizing performance in parallel processing environments. It highlights two predominant frameworks for multiprocessor communication: shared address space and multiple address spaces.

In systems utilizing a **shared address space**, processors communicate implicitly through load and store operations, thereby accessing the same memory directly. Conversely, **multiple address spaces** employ **message passing**, where processors exchange explicit messages to coordinate actions or share data. This message passing approach is particularly relevant in **message passing multiprocessors**, which facilitate communication across distinct memory spaces.

There are two main types of message passing techniques: **synchronous** and **asynchronous**. Synchronous communication requires the initiating processor to wait for a response before proceeding, whereas asynchronous

communication allows the sender to continue its processes without waiting for a reply. While libraries like MPI (Message Passing Interface) enhance program portability, they may inadvertently reduce performance due to their generalized interface.

Performance in multiprocessor communication hinges on three crucial metrics:

- 1. **Communication Bandwidth**: The maximum data transfer rate, influenced by the efficiency of the interconnection network and occupancy during communication.

- 2. **Communication Latency**: The time delay involved in message delivery, where high latency can be detrimental to overall performance and complicate programming tasks.

- 3. **Latency Hiding**: The capability to overlap communication with computation, effectively minimizing the perceived delays in data transfer.

The chapter addresses the challenges associated with parallel processing, prominently framed by **Amdahl's Law**, which identifies two significant barriers: the inherent limits of program parallelism and the high costs associated with communication. It illustrates that the speedup achievable with multiple processors is confined by the portion of the program that can execute in parallel. Furthermore, latency in accessing remote memory can be steep, ranging from 100 to 1000 clock cycles, exacerbating performance challenges.

Understanding application characteristics is pivotal in overcoming these challenges. Factors like **load balance**, **data distribution**, and **memory access patterns** play critical roles in optimizing parallel algorithms and improving efficiency.

In assessing communication mechanisms, the chapter outlines their respective advantages:

# 1. Shared Memory:

- Integrates seamlessly with existing centralized systems.

- Simplifies programming, particularly for complex communication patterns.

- Offers lower overhead for small data transfers and leverages hardware-controlled caching effectively.

# 2. Message Passing:

- Can lead to simpler hardware architecture.

- Clarifies communication pathways for developers, reducing potential for errors.

- Naturally aligns with the need for synchronization, enhancing reliability in data sharing.

In conclusion, the chapter underscores that both shared memory and message passing each come with distinct benefits and challenges. The optimal choice of communication mechanism is contingent upon a comprehensive understanding of the application domain, communication requirements, and the specific architecture of the multiprocessor. Current research is directed towards enhancing communication latency and developing flexible communication models to further boost parallel processing efficiency.

# Install Bookey App to Unlock Full Text and Audio

Free Trial with Bookey

# unlock your potencial

Free Trial with Bookey

Scan to download

funds for Blackstone's firs overcoming numerous reje the importance of persister entrepreneurship. After two successfully raised \$850 m **Chapter 17 Summary: CPI = 0.5 + 0.8 = 1.3**

Chapter 17: Summary of Multiprocessors and Thread-Level Parallelism

This chapter delves into the performance and characteristics of multiprocessor architectures, focusing on their application in commercial and scientific workloads. It begins by examining three primary commercial applications: Online Transaction Processing (OLTP), Decision Support Systems (DSS), and a web index search benchmark called Altavista. Each application reflects unique memory access behaviors and CPU usage patterns:

- 1. **OLTP**: Notable for its high I/O latency and significant server blocking, OLTP is essential for handling transactions efficiently, requiring quick data access and processing.

- 2. **DSS**: This system leverages parallelism within and across queries, resulting in reduced blocking calls and better performance in data analysis tasks.

- 3. **Altavista**: Designed for memory-mapped database operations, this application minimizes synchronization overhead between threads, thus optimizing speed and efficiency.

The chapter further discusses the implications of high contention in

bus-based symmetric shared-memory architectures. These systems, which facilitate cache coherence and synchronization among processors, may encounter delays in memory access during high usage, leading to performance bottlenecks.

Multiprogramming and OS Workload are also addressed, where multiple processes operate concurrently. This requirement emphasizes the importance of maintaining CPU efficiency and optimizing memory access to enhance overall performance.

Transitioning to **Scientific Applications**, the chapter highlights specific computational tasks—such as Fast Fourier Transform (FFT) and LU decomposition—demonstrating how I/O demands affect performance in compute-intensive scenarios. Applications like Barnes and Ocean illustrate the potential for harnessing high parallelism to improve results.

The discussion on the **Performance of Symmetric Shared-Memory Multiprocessors** reveals that synchronization can become a critical bottleneck, particularly in larger systems. This emphasizes the need for advanced locking mechanisms and strategies to reduce serialization and enhance throughput.

In terms of **Synchronization Mechanisms**, the chapter introduces various strategies, including spin locks and barriers. Spin locks, while effective for

managing access control through atomic operations, can lead to inefficiencies under high contention due to increased bus traffic. Hardware primitives serve as a basis for building efficient locking systems, whereas software-driven solutions like queuing locks can alleviate contention and enhance lock acquisition times.

In conclusion, the chapter asserts that optimizing thread-level parallelism and refining synchronization mechanisms are vital for improving the performance of multiprocessor systems. Meticulously designed hardware and software layers are essential to maximize resource utilization while minimizing the challenges associated with contention and memory latency in distributed shared-memory architectures.

Chapter 18 Summary: struct node{/\* a node in the combining tree \*/ int counterlock; /\* lock for this node \*/ int coun...

### Chapter 18 Summary of "Computer Architecture" by John L. Hennessy

# **Synchronization in Multiprocessors**

In multiprocessor systems, synchronization is critical for efficient operation and can encounter two types of contention: read contention, where multiple processors attempt to read the same data simultaneously, and write contention, occurring when multiple processors try to write data at the same time. To manage this contention and minimize serialization—the slowing of processes waiting for access—a structure known as combining trees is utilized. This structure aggregates multiple requests in a tree format, effectively controlling processes that wait on releasing a synchronization flag.

# **Hardware Synchronization Primitives**

Two fundamental synchronization methods are used in multiprocessing systems: locks and barriers. Traditional lock implementations can inadvertently create high levels of contention, hampering performance.

Advanced methods such as queuing locks help address this issue by enabling waiting processors to be handed off the lock in an organized manner, thus reducing contention. An efficient operation known as fetch-and-increment further aids in synchronization by atomically fetching a value and incrementing it. This method enhances scalability during synchronization tasks compared to traditional locking mechanisms.

### **Memory Consistency Models**

Memory consistency is vital in multiprocessor systems, with the sequential consistency model ensuring that memory accesses are strictly ordered. However, this can often be inefficient. More flexible models like processor consistency relax certain constraints, leading to improved performance, albeit introducing potential complications for programming.

# **Multithreading**

Within the realm of execution, multithreading is categorized into two types: fine-grained and coarse-grained multithreading. Fine-grained multithreading switches contexts at every instruction, effectively minimizing delays but possibly slowing the performance of individual threads. Coarse-grained multithreading, in contrast, switches threads during longer idle periods, which is more effective for longer stalls. Simultaneous multithreading (SMT) merges thread-level parallelism (TLP) and instruction-level

parallelism (ILP) to maximize resource usage within a processor, significantly enhancing throughput.

### **Memory System Issues**

Many multiprocessors utilize multilevel caches that observe the inclusion property, ensuring consistency across different cache levels. Nonblocking caches are another innovative solution, allowing processors to send multiple memory requests simultaneously, which can help mitigate latency and accommodate weaker memory consistency models effectively.

### **Cost and Pricing Trends**

The chapter further explores the intricate relationship between price and cost. While pricing reflects manufacturing costs, it is also swayed by market factors such as demand and competition. Production volume plays a crucial role too; higher production volumes can reduce the per-unit cost through efficiencies gained in manufacturing processes and learning over time.

# **Measuring Performance**

Accurately measuring performance in multiprocessor systems is complex due to varying workloads, processing times, and the responsiveness of memory systems. Two key metrics—throughput and response time—provide

essential insights into performance effectiveness. Benchmarking plays a significant role here, with standardized tests such as SPEC and TPC benchmarks providing critical data to assess performance across various computing environments.

### **Instruction Set Architecture (ISA)**

The chapter reviews the historical context of the Instruction Set Architecture (ISA), highlighting that many foundational design decisions still influence contemporary systems. AS instruction sets evolve, they continue to adopt new features and optimizations tailored to the dynamic landscape of applications and programming needs.

### **Conclusion**

In summary, this chapter underscores the multifaceted complexity involved in computer architecture design. It traverses themes of synchronization, memory consistency, multithreading, costs, performance measurement, and ISA evolution, illustrating the dynamic interplay between advancing hardware capabilities and the ever-changing demands of software in today's computing ecosystems.

Chapter 19 Summary: Assume that when i processors are in use, the application runs i times faster. Rewrite

Amdahl's ...

Chapter 19 Summary: Multiprocessors and Thread-Level Parallelism

Introduction

This chapter explores the evolution and critical role of multiprocessor systems in enhancing computational performance, particularly through a technique known as thread-level parallelism (TLP). This method allows multiple threads to execute simultaneously, leveraging the capabilities of multiple processors to achieve greater efficiency.

Amdahl's Law

A foundational principle presented in this chapter is Amdahl's Law, which delineates the theoretical limits on the speedup that can be achieved through parallel processing. It clarifies that not all tasks can be parallelized equally; some parts of a task remain serial and, therefore, impose a cap on overall performance improvements. The chapter includes mathematical formulas and models to help readers compute expected performance gains, acknowledging both the parallel and serial components of workloads.

### **Transactional Processing Council (TPC) Benchmarks**

To better comprehend the performance landscape of various multiprocessor systems, the chapter highlights the importance of analyzing benchmarks established by the Transactional Processing Council (TPC). These benchmarks provide valuable insights into how different architectures—such as Symmetric Multiprocessing (SMP), Non-Uniform Memory Access (NUMA), and clustered systems—perform under diverse metrics, including price and performance efficiency.

### **Top 500 Supercomputers**

Further, the chapter emphasizes the significance of the Linpack benchmark, which ranks the world's most powerful supercomputers. By examining these rankings, readers can appreciate the diversity among supercomputer configurations and gauge their performance relative to their cost, thereby understanding the competitive landscape of high-performance computing.

# **Cache Coherence in Multiprocessors**

A critical technical aspect discussed is cache coherence in multiprocessor systems. The chapter details the use of write-through caches in small bus-based multiprocessors, which simplify coherence protocols. It contrasts

traditional snooping cache coherence protocols with the functionalities of write-through caches, offering insight into how data consistency is maintained across multiple processors.

# Conclusion

In conclusion, the chapter underlines the imperative to optimize architectures for parallel processing. By doing so, computing efficiency can be significantly enhanced across a variety of applications, from scientific endeavors to commercial services, thereby maximizing the benefits of multiprocessor systems and TLP.

# Chapter 20: One possible approach to achieving the scalability of distributed shared memory and the cost-effe...

### Summary of Chapters

In exploring the evolution of cache-coherence protocols, several groundbreaking enhancements have been proposed to improve their efficiency in handling cache states and maintaining performance across processor architectures.

# 6.16 Write-back Cache

To optimize basic snooping cache-coherence protocols, the introduction of a clean private state is proposed. This innovation allows for better management of cache states, facilitating more efficient data retrieval and processing across multiple processors, thus enhancing overall system performance.

# **6.7 Valid Bit Implementation**

Addressing the challenge of false sharing, a solution involving the implementation of a valid bit per word or byte is introduced. This allows for

selective invalidation of individual words within a cache block, enabling different processors to perform separate write operations without compromising the integrity of shared data. While this enhancement holds great promise, it complicates the underlying snooping coherency protocol, necessitating careful consideration of its integration to maintain system reliability and efficiency.

### 6.8 Performance Analysis of Write Invalidate and Write Update Schemes

A detailed performance analysis distinguishes write invalidate and write update schemes based on bandwidth usage and latency. Various code sequences are presented to illustrate the bandwidth advantages of each scheme under specific conditions. Furthermore, the latency benefits of update schemes are highlighted in contrast to invalidate schemes, although it is also noted that contention among processors can lead to increased latency in update contexts. This nuanced understanding of performance dynamics is crucial for system architects in choosing appropriate strategies for cache management.

# **6.9 Miss Rates and AMAT Analysis**

The relationship between miss rates, block sizes, and their impact on Average Memory Access Time (AMAT) is analyzed using data from scientific applications. This analysis requires careful consideration of

parameters such as memory access times based on varying block sizes, ultimately providing valuable insights into optimizing memory efficiency in high-performance computing environments.

### **6.10** Scalability of Distributed Shared Memory